kongruxue

Newbie level 6

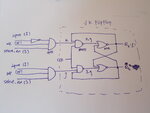

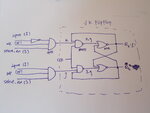

Hi, I want to get the gate circuit which shows in the handwrite gate circuit

.

.

so I wrote the VHDL code below

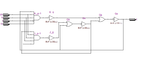

and I check the RTL Viewer, I get the image

but not the same, How do I change the code?

.

. so I wrote the VHDL code below

Code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY memory_cell IS

PORT

( I :IN std_logic;----input bit

W :IN std_logic;-----write_enable

S :IN std_logic;----select_enable

clk :IN std_logic;

q :OUT std_logic------output bit

);

END memory_cell;

ARCHITECTURE structural OF memory_cell IS

SIGNAL J,K,J_g,K_g,Qa,Qb :std_logic;

ATTRIBUTE keep : boolean;

ATTRIBUTE keep OF J_g,K_g,Qa,Qb: SIGNAL IS true;

BEGIN

K <= NOT I AND W AND S;

J <= I AND W AND S;

K_g <= NOT (K AND clk AND Qa);

J_g <= NOT (J AND clk AND Qb);

Qa <= K_g NOR Qb;

Qb <= J_g NOR Qa;

q <= Qa;

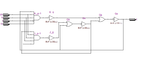

END structural;and I check the RTL Viewer, I get the image

but not the same, How do I change the code?