Crusader370

Junior Member level 1

- Joined

- Jun 19, 2006

- Messages

- 17

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- montreal, canada

- Activity points

- 1,425

Hi All,

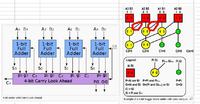

We have a project to implement an 8-bit carry lookahead adder in cmosp18 technology. Do you have any suggestions on what type of logic to use? At the moment, we are thinking of implementing a logarithmic adder (Kogge-Stone) in static CMOS, but one thing that we noticed is that we have way too many inverters in our critical, and other, paths.

Do you have any suggestions for us? Did we choose the right path?

Thanks,

Crusader

P.S. Oh yes, and the criteria is that it is supposed to be as fast as possible.

We have a project to implement an 8-bit carry lookahead adder in cmosp18 technology. Do you have any suggestions on what type of logic to use? At the moment, we are thinking of implementing a logarithmic adder (Kogge-Stone) in static CMOS, but one thing that we noticed is that we have way too many inverters in our critical, and other, paths.

Do you have any suggestions for us? Did we choose the right path?

Thanks,

Crusader

P.S. Oh yes, and the criteria is that it is supposed to be as fast as possible.