Shishira

Junior Member level 2

- Joined

- Jun 8, 2018

- Messages

- 20

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Dresden, Germany

- Activity points

- 229

Hi All,

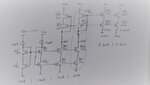

I am designing a reference circuit for the current steering DAC. The current provided is 10 uA and I need a current of 500nA as LSB current. I decided to take up PMOS based DAC with nmos cascode current mirror as its reference (as shown in the figure).

I was able to achieve the design working untill nmos stage, giving 2uA to Pmos counterpart. When I stack pmos cascode over nmos cascode(highlighted in the figure), the pmos cascode pair in the rail isn't biased. I have mentioned the W/L ratios in the figure.

1) By simulation I see that most of the Vdd is consumed by nmos cascode transitor (Vds), why ?

2) How do I properly bias the upper 2 pmos transistors when they are stacked above 2 nmos tranisitors.