iaf

Member level 3

Hello, i have a digital output with varying pulse sizes and i want to stretch the 0 output for a constant T+ 0 pulse time. I have tried using a monostable multivibrator with a NAND gate but the problem i got is that the length of the pulse remains constant, which could be a problem if the pulse width is greater than the multivibrator output so how to add this time constant to the original pulse width instead?

- - - Updated - - -

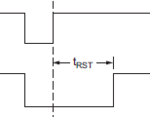

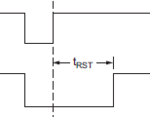

here's an image of the desired output

- - - Updated - - -

here's an image of the desired output