Junus2012

Advanced Member level 5

Dear friends

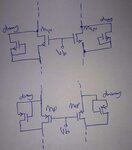

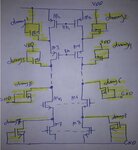

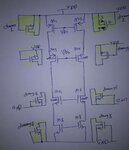

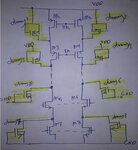

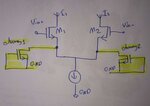

I am matching my circuit layout with dummies connected as shown below. I am connecting the dummy transistor as usual instance in the schematic circuit so the LVS will not complain when he compare.

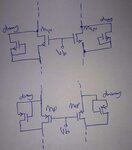

I see this connection from one website but I am wondering that this dummy connection would add parasatic capacitance to the node where it is connected.

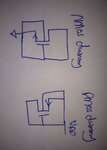

Is it possible to avoide this connection with other type, for example using PMOS with gate, source and drain tied together and connected to Vdd, for the NMOS gate, source and drain tie together and connected to gnd

Thank you in advance

I am matching my circuit layout with dummies connected as shown below. I am connecting the dummy transistor as usual instance in the schematic circuit so the LVS will not complain when he compare.

I see this connection from one website but I am wondering that this dummy connection would add parasatic capacitance to the node where it is connected.

Is it possible to avoide this connection with other type, for example using PMOS with gate, source and drain tied together and connected to Vdd, for the NMOS gate, source and drain tie together and connected to gnd

Thank you in advance