troy99xx

Newbie level 6

I have a parallel bus of 32 bits changing value on every clock cycle @ 50 mhz

I need to detect pattern 0111111111111111111111111111111 [31..0] (bit 31 is a zero)

The pattern can start at any bit position of the parallel bus

This mean that I can get the 'zero bit" on i.e bit 19 of the parallel bus and I will have to look at the previous word to get the full 31 bits of '1"

example

.....Bus . 31..0

clk_0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

clk_1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

clk_2 ...

The pattern is in bold.

After the pattern is detected, I am immediately required to look for another pattern on bit 20 of clk_1

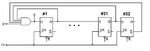

I was thinking about a shift register but I can't serialize fast enough to look for pattern and keep the old data...

Can someone help with some pointers of how I can do this

I will have fifo to go from the 49 Mhz clock domain to a 133MHZ clock

thank you

I need to detect pattern 0111111111111111111111111111111 [31..0] (bit 31 is a zero)

The pattern can start at any bit position of the parallel bus

This mean that I can get the 'zero bit" on i.e bit 19 of the parallel bus and I will have to look at the previous word to get the full 31 bits of '1"

example

.....Bus . 31..0

clk_0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

clk_1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

clk_2 ...

The pattern is in bold.

After the pattern is detected, I am immediately required to look for another pattern on bit 20 of clk_1

I was thinking about a shift register but I can't serialize fast enough to look for pattern and keep the old data...

Can someone help with some pointers of how I can do this

I will have fifo to go from the 49 Mhz clock domain to a 133MHZ clock

thank you