hyleeinhit

Member level 3

Hi,

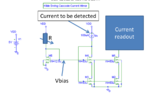

In the attached figure for wide wing current mirror, M1 and M4 are bias by M5 and resistor R. Resistor R is a variableoff chip resistor. Call this as method 1.

In method 2, directly bias M1 and M4 with an off-chip variable voltage generator (two-resistor divider)+buffer.

Which one has better noise performance? And which one is better from your experience?

In the attached figure for wide wing current mirror, M1 and M4 are bias by M5 and resistor R. Resistor R is a variableoff chip resistor. Call this as method 1.

In method 2, directly bias M1 and M4 with an off-chip variable voltage generator (two-resistor divider)+buffer.

Which one has better noise performance? And which one is better from your experience?

Attachments

Last edited: