Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

The first mask is the active (TOX) definition mask. In order to compensate for possible displacement between this previous active and the following poly gate masking, there's a finite overlap of poly necessary (and stipulated by design rules), called poly cap.1. If there is no poly cap, then poly ends (up/down) will align with diffusion edges. Why it is not done? What problem it might create?

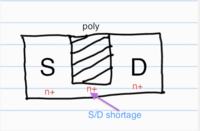

Obviously a (partly) continuous n+ or p+ region would be created, shorting S and D.2. If poly is smaller than the diffusion (device) width, what problem it might cause?

Hope I can make it clear with the help of this shorted nMOSFET:I can't get the idea of S/D shorting. Please explain.

Poly cap - also called poly extension or poly overhang - is needed against mis-alignment between active area (thin oxide definition) and poly, and the later following S/D implant.So you mean that poly cap is only needed for poly and S/D alignment

I think you're mixing up two different alignment occurrences: self-alignment and (possible) mis-alignment. Both are concerned:... as it's a self aligned process? But the alignment occurs along the length, not along the width. So again can't get the idea properly.

... is there only one mask for S and D region. And poly edge decides the channel-wise spacing between S/D region. Am I right?