kabaleevisu

Advanced Member level 2

- Joined

- Apr 14, 2010

- Messages

- 616

- Helped

- 85

- Reputation

- 170

- Reaction score

- 81

- Trophy points

- 1,308

- Location

- Chennai,India

- Activity points

- 4,512

Hi everyone,

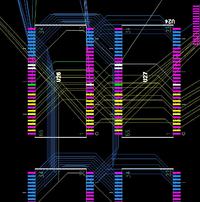

Right now in my design i am MCF548x ColdFire® Microprocessor using before placing the processor and ddr i need to clarify some thing

what is topology ?? topology is very depends on placement ??

who will decide topology (hardware designer or pcb designer )

which topology is best for ddr board ?

i have the reference document but i could not find answer

i need help from anyone......!

Right now in my design i am MCF548x ColdFire® Microprocessor using before placing the processor and ddr i need to clarify some thing

what is topology ?? topology is very depends on placement ??

who will decide topology (hardware designer or pcb designer )

which topology is best for ddr board ?

i have the reference document but i could not find answer

i need help from anyone......!

Last edited: