chaojixin

Member level 1

Hi, every one!

I'm on the design of a 2.5~4.2V input, 1.8V output, 400mA LDO(CMOS process), and a over-current protection is needed.

What's the most used method in product?

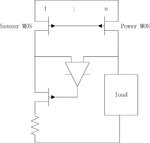

the academic papers usually present a current mirror method as shown in the figure but I think the mismatch is high because the 'n' is always 1000 or even larger. does the product always use this method?

I'm on the design of a 2.5~4.2V input, 1.8V output, 400mA LDO(CMOS process), and a over-current protection is needed.

What's the most used method in product?

the academic papers usually present a current mirror method as shown in the figure but I think the mismatch is high because the 'n' is always 1000 or even larger. does the product always use this method?

Attachments

Last edited: