MammPp

Junior Member level 2

Dear All,

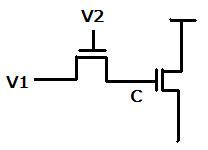

I have some question about floating node. As the following picture,

If I set V1 to be Vdd all the time.

and V2 is Vdd at the first period, then set V2 is 0 (Which is close NMOS)

My question is, what is the value of the voltage at node C ?

and if V2 is zero, the other transistor, which node C is gate of them, is on/off ?

Thank you so much for your help

MammPp

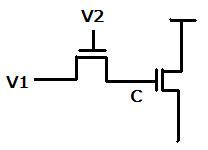

I have some question about floating node. As the following picture,

If I set V1 to be Vdd all the time.

and V2 is Vdd at the first period, then set V2 is 0 (Which is close NMOS)

My question is, what is the value of the voltage at node C ?

and if V2 is zero, the other transistor, which node C is gate of them, is on/off ?

Thank you so much for your help

MammPp