heythem2008

Newbie level 6

- Joined

- Jul 9, 2008

- Messages

- 14

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- sherbrooke, canada

- Activity points

- 1,373

Hi, this is the first time that i participate in this forum and i hope that u can help me.

I have created a FIFO with the Megawizard of QUARTUS II.

I have used a double clock FIFO with 2 bit input, a write_request, a read_request, write_empty and read_empty signals.

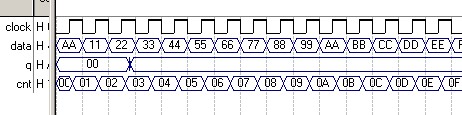

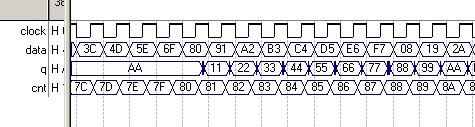

I tried to simulate i have seen how the write empty has changed but my problem that i cant read the data from the FIFO (output)

I join my schematic and the simulation to give me your help

Thank you.

I have created a FIFO with the Megawizard of QUARTUS II.

I have used a double clock FIFO with 2 bit input, a write_request, a read_request, write_empty and read_empty signals.

I tried to simulate i have seen how the write empty has changed but my problem that i cant read the data from the FIFO (output)

I join my schematic and the simulation to give me your help

Thank you.