abhishek.2138

Full Member level 2

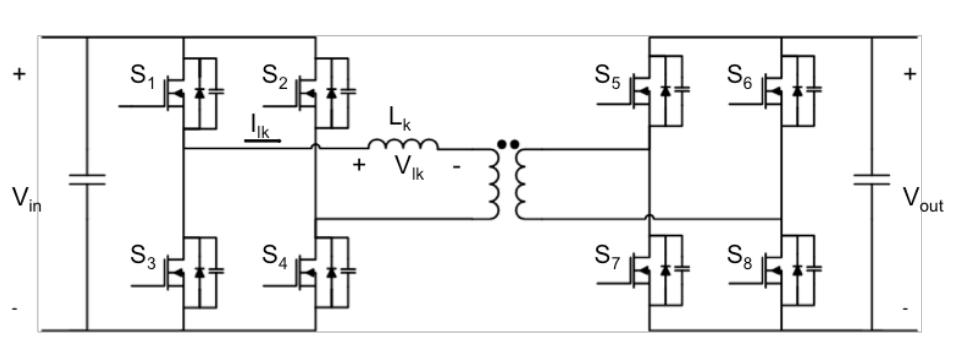

How to calculate the dead time in dual active bridge converter?

Pls refer reference schematic.

MOSFET ON time = 70ns.

Frequency = 100 kHz.

Duty cycle = 50%.

Magnetizing inductance = 720uH

Leakage inductance = 22uH

Input DC voltage = 800V

Output DC voltage = 450V

Pls refer reference schematic.

Last edited: