Junus2012

Advanced Member level 5

Dear friends

I have some issues with the seal-ring design.

We are working on XFAB XH035 µm technology.

We have installed the seal ring Pcell by following the steps from "User Guide Implementation of

Peripheral Ring – Design kit in Cadence".

The Pcell is successfully added to Cadence and also we confirmed the structure by analyzing the cell with respect to the seal ring design rules given by "Design Rule Overview XH035 –Multi-Project Designs Document DR_SR_XH035 Release 1.2.0"

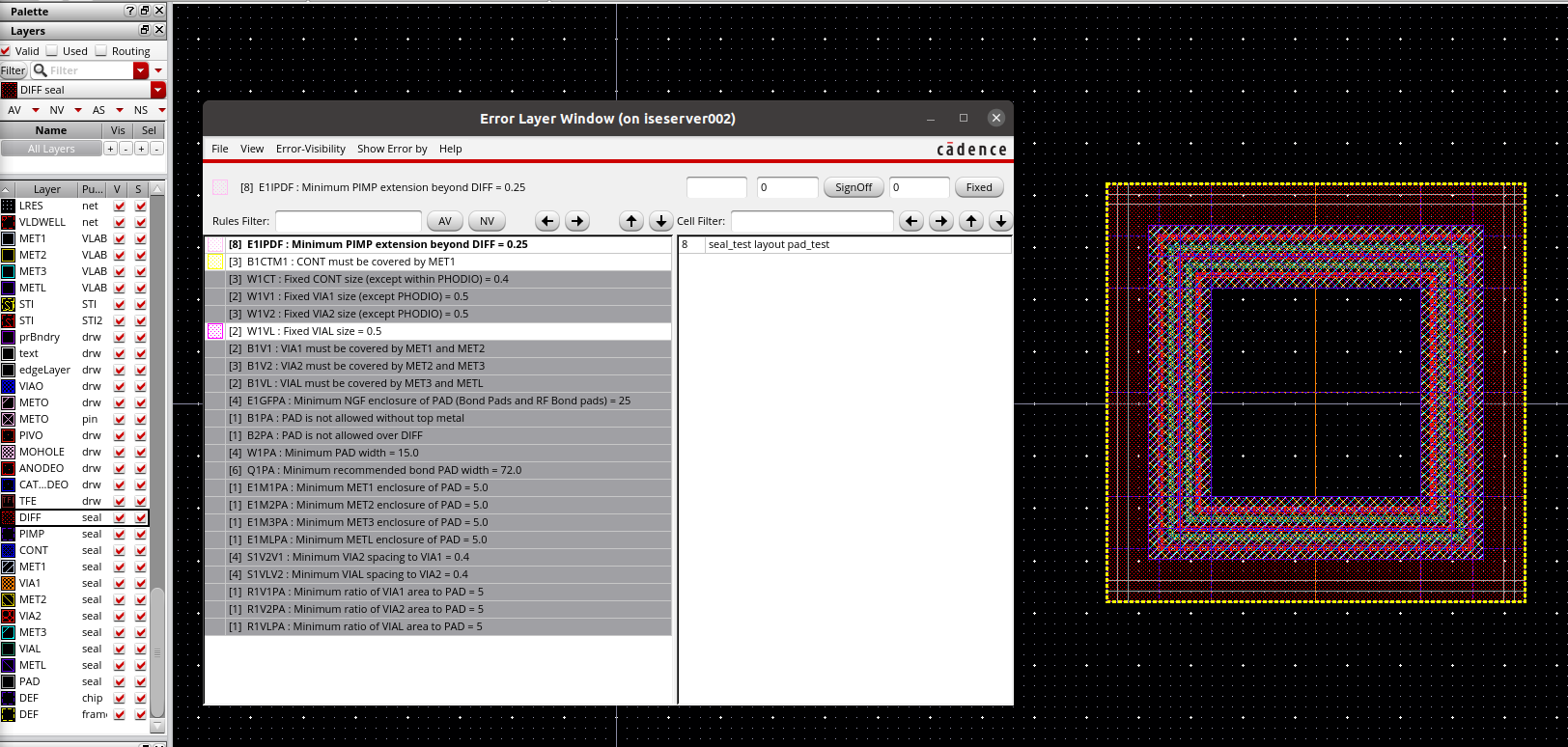

After surrounding our prototype chip with the seal ring we received numerous DRC errors,

On our way to investigate the reason we have created a new layout cell and only inserting the seal-ring Pcell and by running DRC over it the same amount of errors are generated. It looks to us that Pcell itself is not DRC clean as it is supposed. Also, it looks that DRC is confusing between the seal type metals and the metal draw-type used in the technology.

I have taken a snapshot of the DRC error and attached it to the email.

We are also thinking that we might not need to run the DRC over the seal ring.

The last issue is relevant as well since we want to connect the seal ring to the chip ground PAD, the metals used in the chip core and PAD are type "draw", for example, MET draw, while for the ring is type seal. How to connect between them.

I am are looking forward to your kind help

Best Regards

I have some issues with the seal-ring design.

We are working on XFAB XH035 µm technology.

We have installed the seal ring Pcell by following the steps from "User Guide Implementation of

Peripheral Ring – Design kit in Cadence".

The Pcell is successfully added to Cadence and also we confirmed the structure by analyzing the cell with respect to the seal ring design rules given by "Design Rule Overview XH035 –Multi-Project Designs Document DR_SR_XH035 Release 1.2.0"

After surrounding our prototype chip with the seal ring we received numerous DRC errors,

On our way to investigate the reason we have created a new layout cell and only inserting the seal-ring Pcell and by running DRC over it the same amount of errors are generated. It looks to us that Pcell itself is not DRC clean as it is supposed. Also, it looks that DRC is confusing between the seal type metals and the metal draw-type used in the technology.

I have taken a snapshot of the DRC error and attached it to the email.

We are also thinking that we might not need to run the DRC over the seal ring.

The last issue is relevant as well since we want to connect the seal ring to the chip ground PAD, the metals used in the chip core and PAD are type "draw", for example, MET draw, while for the ring is type seal. How to connect between them.

I am are looking forward to your kind help

Best Regards