fragnen

Full Member level 3

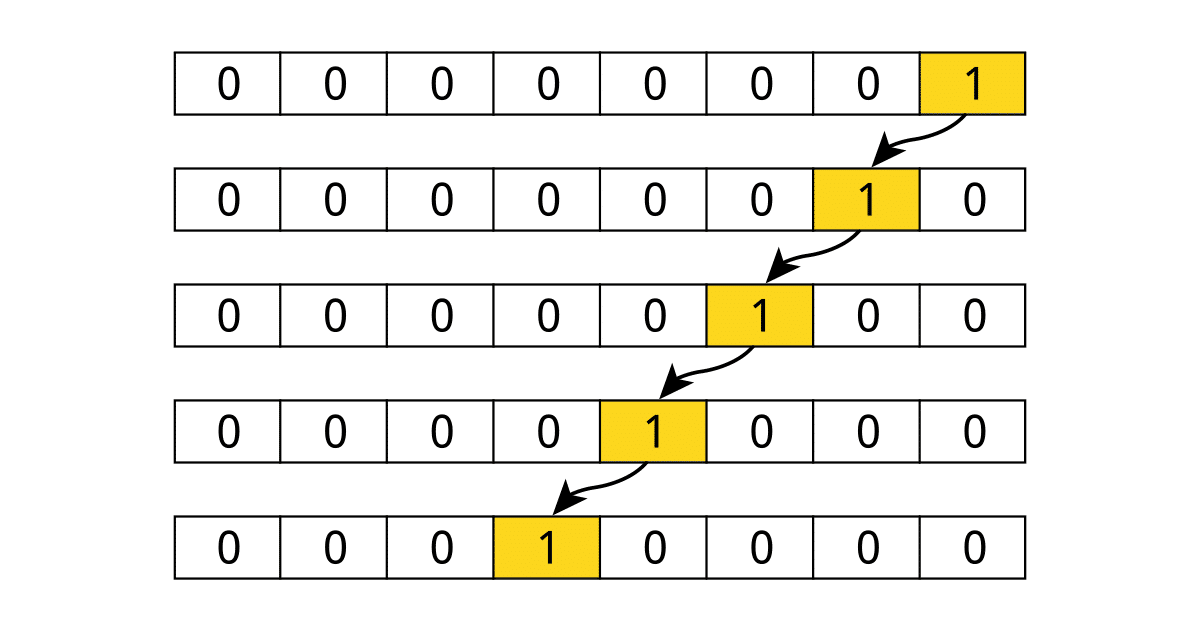

We design sequence detector for sequences having small number of digits like 3,4,6, 7 etc by designing a Mealey or Moore FSM by hand.

How can we design such FSM in hand if the sequence has more number of digits and it is as much as 50 digits or 100 digits?

How can we design such FSM in hand if the sequence has more number of digits and it is as much as 50 digits or 100 digits?