little0192

Newbie level 6

Hi,

I am designing a +/- 10V output DAC board using a current output DAC (PN : AD9767ASTZ).

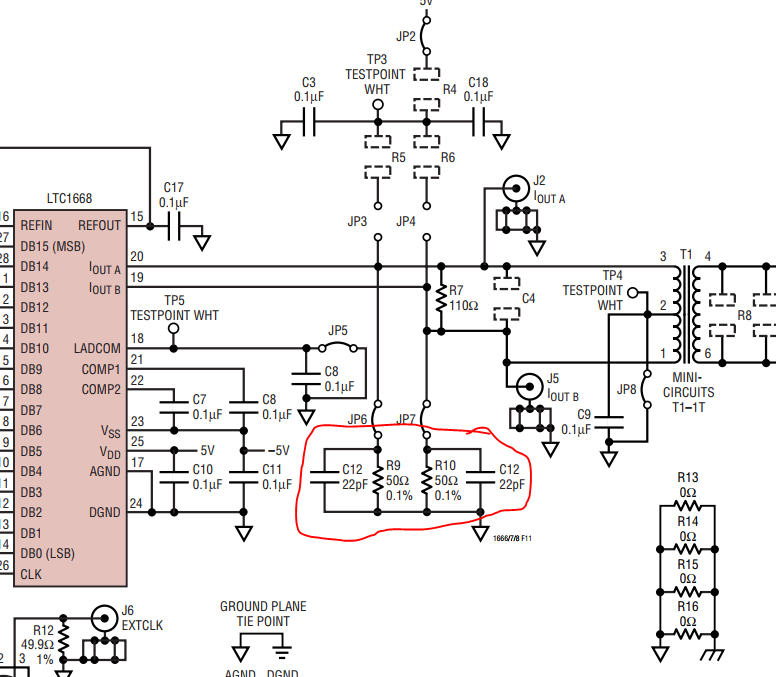

So I am already using a reference design for a Evaluation Board from here. The board can be configured for the different outputs. I am interested in the 3rd type for making +/- 10V signal output.

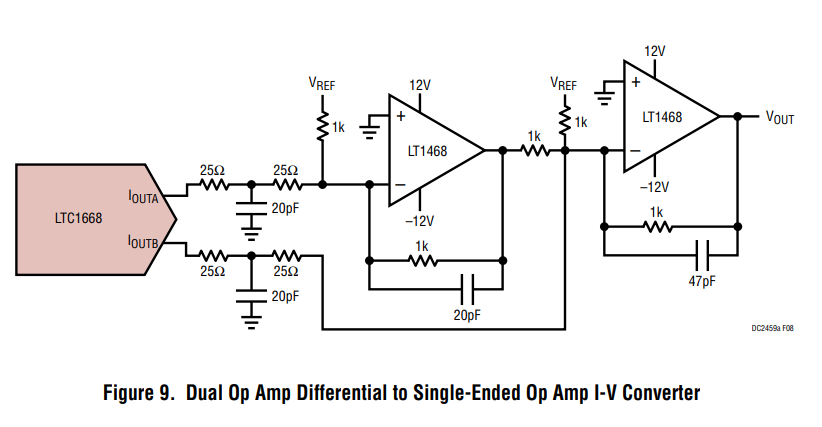

My first question is why they haven't used the 50 ohm parallel termination on the IoutA and IoutB. How is this series arrangement (in the Figure 9 above) functionally different from the parallel termination. However, In the LTC1668 datasheet the suggested circuit has parallel termination only.

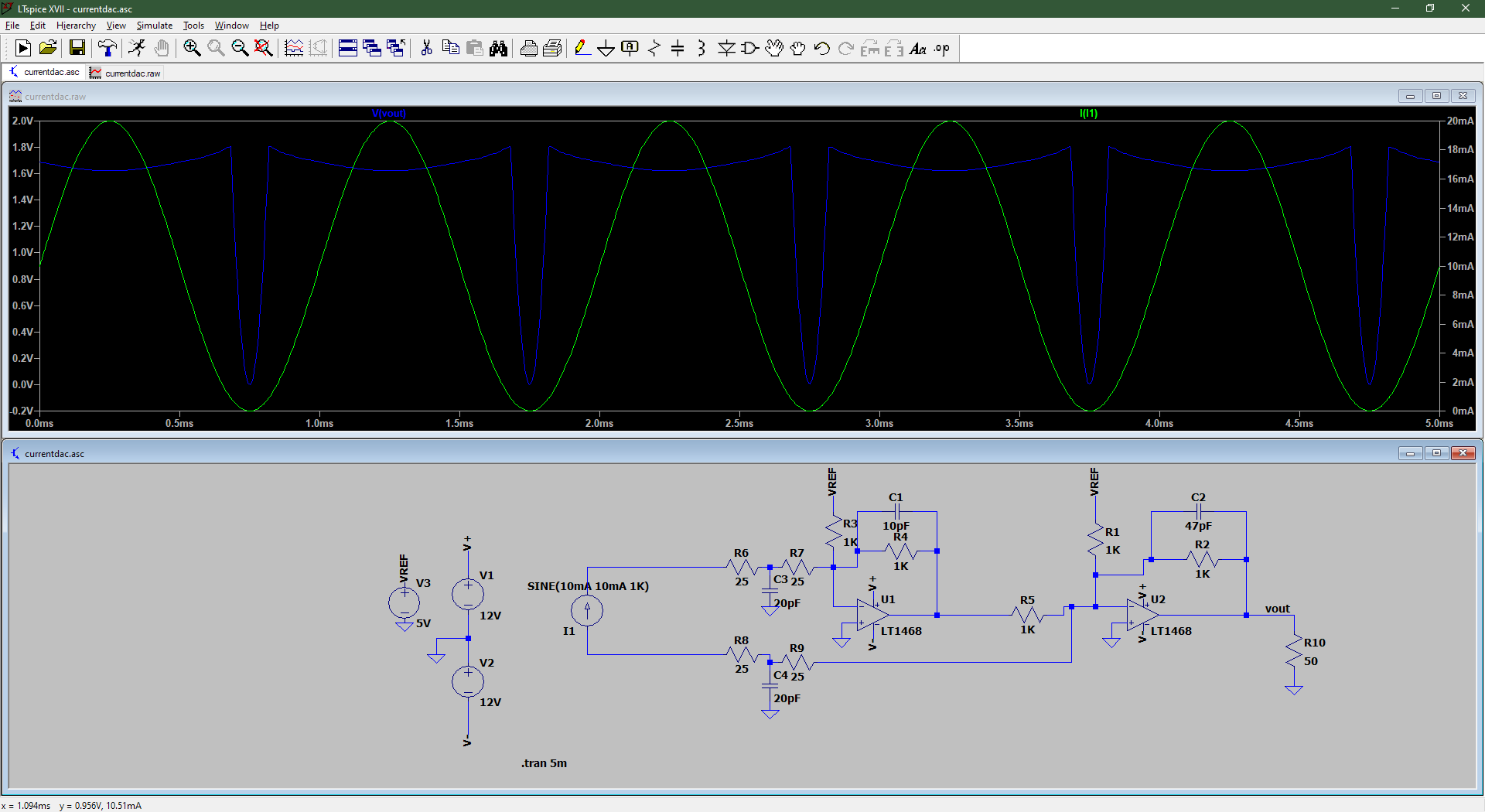

Secondly, I am trying to simulate the circuit in the LTSpice to understand it better. But I am not getting the expected result. Can anyone guide/tell me what I am missing in the simulation? I am using a current source to emulate the Complimentary current output of 0-20mA.

I am attaching the LtSpice Simlation file as well. Thanks .

.

I am designing a +/- 10V output DAC board using a current output DAC (PN : AD9767ASTZ).

So I am already using a reference design for a Evaluation Board from here. The board can be configured for the different outputs. I am interested in the 3rd type for making +/- 10V signal output.

My first question is why they haven't used the 50 ohm parallel termination on the IoutA and IoutB. How is this series arrangement (in the Figure 9 above) functionally different from the parallel termination. However, In the LTC1668 datasheet the suggested circuit has parallel termination only.

Secondly, I am trying to simulate the circuit in the LTSpice to understand it better. But I am not getting the expected result. Can anyone guide/tell me what I am missing in the simulation? I am using a current source to emulate the Complimentary current output of 0-20mA.

I am attaching the LtSpice Simlation file as well. Thanks