promach

Advanced Member level 4

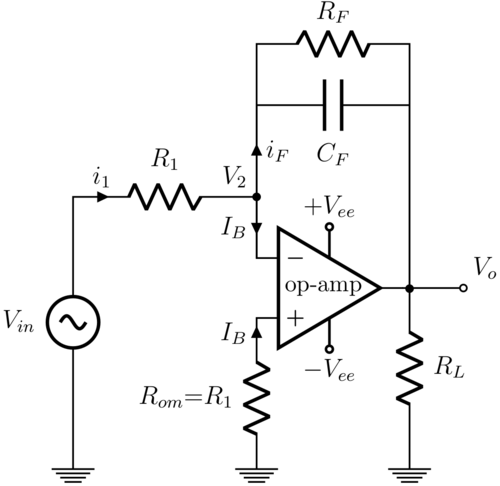

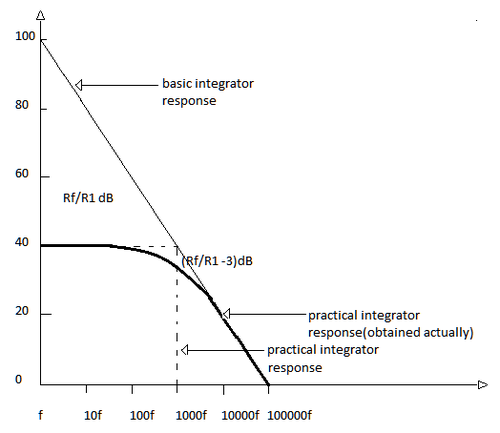

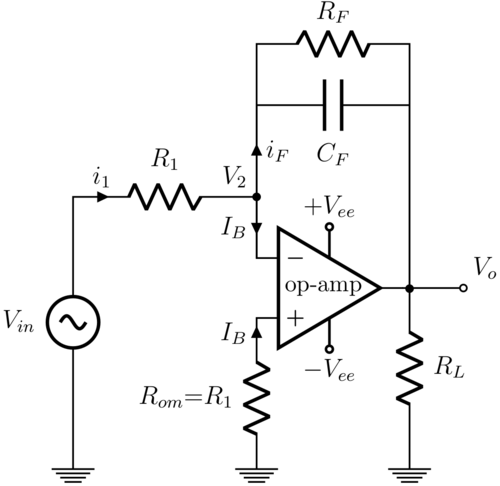

For https://en.wikipedia.org/wiki/Op_amp_integrator#Practical_circuit , why "To negate the effect of the input bias current, it is necessary to set: Ron = R1 || Rf || RL " ? What is Ron ? Is it similar to Rom ?

Why is Rf inside that expression when Rf does not share the same gnd node as RL and R1 ?

Why is Rf inside that expression when Rf does not share the same gnd node as RL and R1 ?