NiedeLu

Junior Member level 3

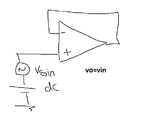

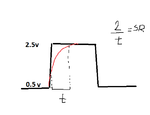

For sure it makes sense to simulate the step response of your design to look at the slew rate and also to check the stability of the system in time-domain. Get your circuitry to the worst condition -> follower. No ringing should occur at the output node.