mrinalmani

Advanced Member level 1

- Joined

- Oct 7, 2011

- Messages

- 463

- Helped

- 60

- Reputation

- 121

- Reaction score

- 58

- Trophy points

- 1,318

- Location

- Delhi, India

- Activity points

- 5,285

Hi

I have a hard switched MOSFET bridge running at 100KHz.

The output capacitance is nearly 5nF and the ringing frequency at transients is 48MHz.

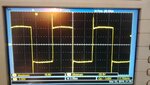

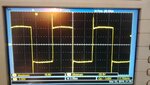

After snubbing the FETs with an RC snubber of 20nF and 1 Ohm, ringing is damped out but a small spike of around 2V remains.

However when I begin to load the bridge, the spike rises to over 15V at 25A current.

No value of resistance or capacitance seems to suppress this spike.

The two photos show the output at 10A load and 25A load.

The bridge drives a 12V : 240V transformer with approx 100nH leakage. The HV side of the transformer is connected directly to a resistive load without rectification.

How to solve this? Please help

I have a hard switched MOSFET bridge running at 100KHz.

The output capacitance is nearly 5nF and the ringing frequency at transients is 48MHz.

After snubbing the FETs with an RC snubber of 20nF and 1 Ohm, ringing is damped out but a small spike of around 2V remains.

However when I begin to load the bridge, the spike rises to over 15V at 25A current.

No value of resistance or capacitance seems to suppress this spike.

The two photos show the output at 10A load and 25A load.

The bridge drives a 12V : 240V transformer with approx 100nH leakage. The HV side of the transformer is connected directly to a resistive load without rectification.

How to solve this? Please help