LvW

Advanced Member level 6

No its 87 .... PM is how much more phase shift is required to make the total phase shift of the system 180. For your case the system phase has already shifted by 93 so to make it unstable it will need 87deg more shift. So the margin left in your system is 87deg .... that is why we call it margin

I am afraid, your contribution is somewhat confusing.

Simulation results are: -180 deg. at DC and 87 deg. at unity gain. Hence, the difference to the stabiluty limit (0 deg or 360deg) is 87 deg. It is wrong to find the difference to 180 deg.

- - - Updated - - -

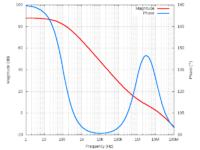

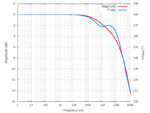

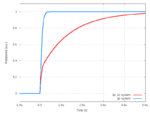

I just measured phase margin of LDO for a different case and now phase margin is 93 degree. But according to post #3, the maximum phase margin is 90 degree.

Is there something wrong here?

anhnha, are you sure? HOW did you measure?

In post#13 the margin was 87 deg - and now it is 180-87=93 deg?

- - - Updated - - -

the PM could be higher than 90 degrees, i.e. when transfer function contains low freq. dominant pole, LHP zero and nondominant pole after a next decade.

Yes - correct. In principle, it is possible that there is a phase enhancement due to a zero - however, I suppose this does not apply to the system under discussion.

Hence, I am not sure if anhnha does simulate the loop gain correctly.