zhangseong

Member level 2

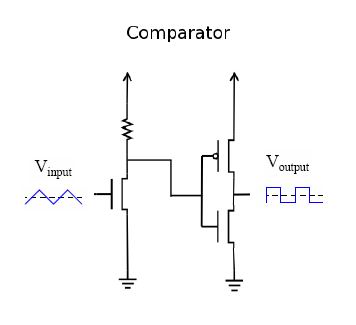

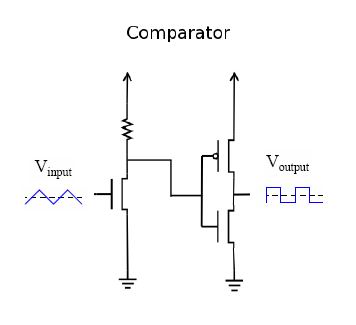

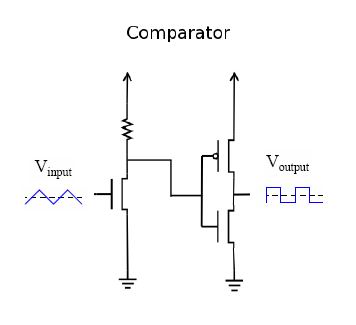

why is this topology is called a comparator ? how the circuit perform , what is the 1st part of the circuit ? is it an inverter?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

hung_wai_ming(at)hotmail.com said:If you need to regard this as comparator, then the trip point is the inverter trip point where it can switch from L to H. Then first stage determines when to turn over when the INPUT is switching from VSS to some point (say, VDD/2) where parallel equivalent resistance of the RDS of NMOS and the up resistor is equal to the trip point of inverter, then the inverter turns from L to H, that's the comparison happens.