anotherbrick

Full Member level 4

- Joined

- Jan 10, 2009

- Messages

- 217

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,298

- Location

- Istanbul , Turkey

- Activity points

- 3,144

hello dear forum

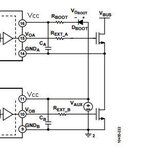

I build a high and low side driver

with HCPL 3120 ( 2 Amps sink source ) optocoupler it is in this picture

the bootstrap cap is 1 uF

( the reverse diode paralel to gate resistor is there but not shown in the picture )

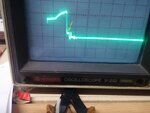

my question ; why cannot the high side pull the gate signal down to 0 V when the high PWM is Off ?

see this picture

thank you

I build a high and low side driver

with HCPL 3120 ( 2 Amps sink source ) optocoupler it is in this picture

the bootstrap cap is 1 uF

( the reverse diode paralel to gate resistor is there but not shown in the picture )

my question ; why cannot the high side pull the gate signal down to 0 V when the high PWM is Off ?

see this picture

thank you