Wanoz

Junior Member level 1

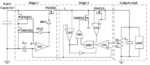

I designed a boost converter in DCM with 90nm CMOS technology. My output should be 3.5V and input is connected to a capacitor through a switch. When cap reaches 1.8V, switch is on and the converter connects to the cap. Once the cap downs to 1V, switch is off. Simulations are carried out in hspice. First current cycle of inductor and output capacitor starts really too high (e.g. 11A) other cycles is really too low (~.6A) (see attached fig. i(cload) output cap current and i(l1) inductor current legends). I don't know why huge gap between current cycles. It should start 0A and then reach max peak current, but in my design it starts 11A. Why this does not start 0A. Also, inductor current and output capacitor current should be matched when NMOS is off and current flows through PMOS or diode. Why these currents are different from each other and output cap current drops to negative value.