nervecell_23

Member level 1

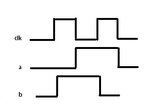

Hello, I've got two questions about using ff triggered by falling edge of the clock:

1) As shown in the figure, if I use both signal a and b to drive the same circuit that is also synchronised to 'clk', is 'a' more stable than 'b'? (Here stable I mean glitch-free)

2) How should I analysis timing for signal 'a'? I mean, for signal 'b', I've got a margin of roughly one clock cycle to accomodate combinatorial logic to avoid timing violation, but for signal 'a', do I only have half-clock cycle to play with if the signal that drives signal 'a' is synchronised to rising edge of the clock?

Thanks.

1) As shown in the figure, if I use both signal a and b to drive the same circuit that is also synchronised to 'clk', is 'a' more stable than 'b'? (Here stable I mean glitch-free)

2) How should I analysis timing for signal 'a'? I mean, for signal 'b', I've got a margin of roughly one clock cycle to accomodate combinatorial logic to avoid timing violation, but for signal 'a', do I only have half-clock cycle to play with if the signal that drives signal 'a' is synchronised to rising edge of the clock?

Thanks.