Junus2012

Advanced Member level 5

Dear friends,

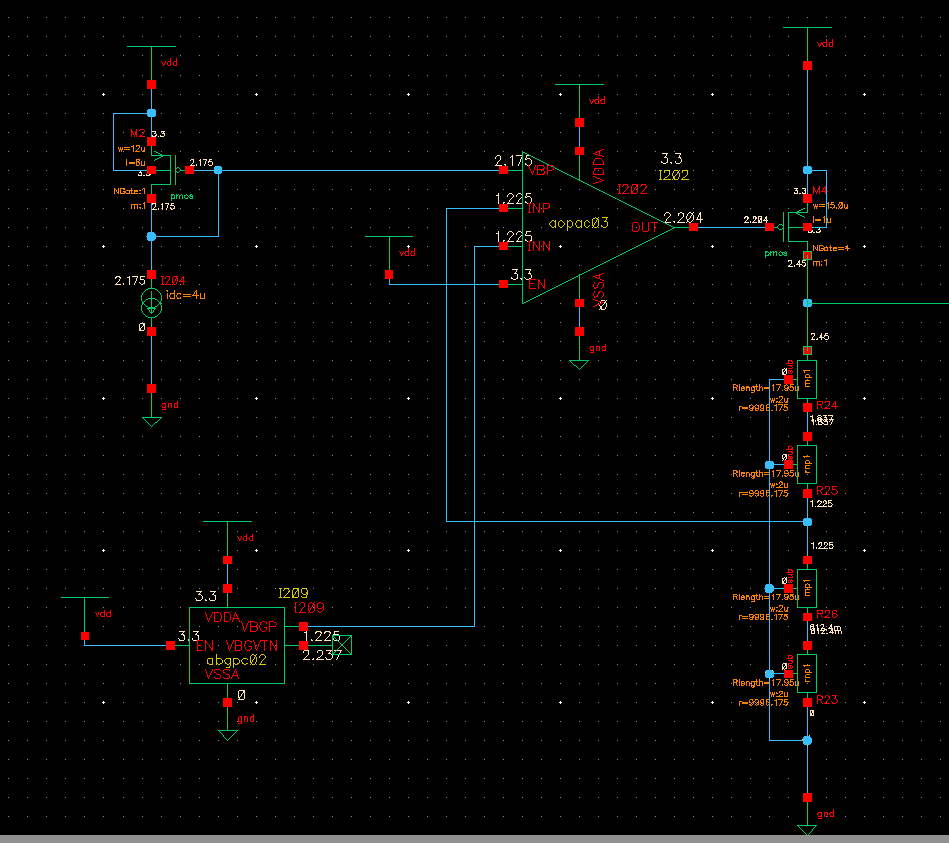

I am using the basic voltage regulator to provide a stable voltage , please see the image below

as in general, it is in principle non-inverting amplifier with input terminal swapped because I used PMOS pass transistor.

here you can see that that the gain is 1+20k*20k = 2, and I connected bandgap reference voltage at the input so the output is 2.45 V, which is perfectly achieved in the circuit DC operation.

I have tried to increase the resistors by using 40 k instead of 20 k, and the result is more vaiation in the regulated output as compared to the former one with 20 k,

Why this is happening?

I tried to be little smart and I connected fat capacitor at the output, and every thing is screwed as I have like oscillated output.

Also I would like to ask you about the pass transistor, what is rule for sizing it?

thank you

I am using the basic voltage regulator to provide a stable voltage , please see the image below

as in general, it is in principle non-inverting amplifier with input terminal swapped because I used PMOS pass transistor.

here you can see that that the gain is 1+20k*20k = 2, and I connected bandgap reference voltage at the input so the output is 2.45 V, which is perfectly achieved in the circuit DC operation.

I have tried to increase the resistors by using 40 k instead of 20 k, and the result is more vaiation in the regulated output as compared to the former one with 20 k,

Why this is happening?

I tried to be little smart and I connected fat capacitor at the output, and every thing is screwed as I have like oscillated output.

Also I would like to ask you about the pass transistor, what is rule for sizing it?

thank you