rx78nt1alex

Newbie level 3

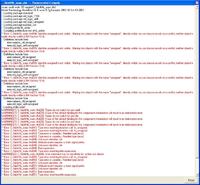

I'm writing a testbench for sram, but i found the port map type in my testbench which does not match to the sram.vhd, i have no idea how to rectify it. Below are the sram design and my testbench design. Could anyone give me some tips how to rectify my testbench in order to test the sram.vhd? Thank you...

-- sram.vhd

Library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

Entity SRAM1 is

Port(

clk,cen,wen : in std_logic;

addr: in unsigned(6 downto 0);

din : in unsigned(31 downto 0);

dout: out unsigned(31 downto 0)

);

End SRAM1;

architecture syn of SRAM1 is

type ram_type is array (127 downto 0) of unsigned (31 downto 0);

signal RAM : ram_type:=(others=>(others=>'0'));

begin

process (clk)

begin

if clk'event and clk = '1' then

if cen='0' then

if wen ='0' then

RAM(to_integer(addr)) <= din;

else

dout <= RAM( to_integer(addr));

end if;

else

dout <= (others => 'Z');

end if;

end if;

end process;

end syn;

--tb_sram.vhd

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

use IEEE.numeric_std.all;

entity TB_ADDER IS

end TB_ADDER;

architecture TEST of TB_ADDER is

component SRAM1 is

Port( clk, cen,wen : in std_logic;

addr: in std_logic_vector(6 downto 0);

din : in std_logic_vector(31 downto 0);

dout: out std_logic_vector(31 downto 0) );

End component;

signal clk_i, cen_i,wen_i : std_logic;

signal addr_i : std_logic_vector(6 downto 0);

signal din_i,dout_i : std_logic_vector(31 downto 0);

begin

DUT: SRAM1 port map (clk_i, cen_i,wen_i,addr_i,din_i,dout_i);

process begin

clk_i<='0';

wait for 5 ns;

clk_i<='1';

wait for 5 ns;

end process;

STIMULUS: process

begin

cen_i<='1';

wen_i<='0';

For i in 0 to 127 loop

din_i<=to_unsigned(i,32);

addr_i<=to_unsigned(i,32);

addr_i <= i; din_i<= i;

wait until(clk'event and clk='1');

End loop;

Wen_i<='1';

For i in 0 to 127 loop

addr_i<=to_unsigned(i,32);

addr_i <= i;

wait until(clk'event and clk='1');

End loop;

end process STIMULUS;

end TEST;

-- sram.vhd

Library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

Entity SRAM1 is

Port(

clk,cen,wen : in std_logic;

addr: in unsigned(6 downto 0);

din : in unsigned(31 downto 0);

dout: out unsigned(31 downto 0)

);

End SRAM1;

architecture syn of SRAM1 is

type ram_type is array (127 downto 0) of unsigned (31 downto 0);

signal RAM : ram_type:=(others=>(others=>'0'));

begin

process (clk)

begin

if clk'event and clk = '1' then

if cen='0' then

if wen ='0' then

RAM(to_integer(addr)) <= din;

else

dout <= RAM( to_integer(addr));

end if;

else

dout <= (others => 'Z');

end if;

end if;

end process;

end syn;

--tb_sram.vhd

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

use IEEE.numeric_std.all;

entity TB_ADDER IS

end TB_ADDER;

architecture TEST of TB_ADDER is

component SRAM1 is

Port( clk, cen,wen : in std_logic;

addr: in std_logic_vector(6 downto 0);

din : in std_logic_vector(31 downto 0);

dout: out std_logic_vector(31 downto 0) );

End component;

signal clk_i, cen_i,wen_i : std_logic;

signal addr_i : std_logic_vector(6 downto 0);

signal din_i,dout_i : std_logic_vector(31 downto 0);

begin

DUT: SRAM1 port map (clk_i, cen_i,wen_i,addr_i,din_i,dout_i);

process begin

clk_i<='0';

wait for 5 ns;

clk_i<='1';

wait for 5 ns;

end process;

STIMULUS: process

begin

cen_i<='1';

wen_i<='0';

For i in 0 to 127 loop

din_i<=to_unsigned(i,32);

addr_i<=to_unsigned(i,32);

addr_i <= i; din_i<= i;

wait until(clk'event and clk='1');

End loop;

Wen_i<='1';

For i in 0 to 127 loop

addr_i<=to_unsigned(i,32);

addr_i <= i;

wait until(clk'event and clk='1');

End loop;

end process STIMULUS;

end TEST;