Ninja13

Junior Member level 2

Hello,

I am simulating a TIA simulation stage followed by a non inverting amplifier stage. Between, there is a RC high pass filter to remove DC value.

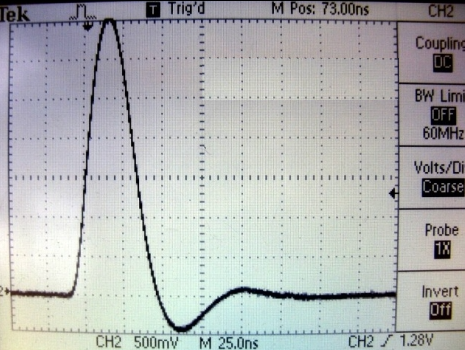

The Fc of that filter is bad chosen (too high compared to the equivalent frequency of the pulse input) and generates a voltage under 0V at the queue of the pulse, as shown below).

This is then the input of the second stage (standard non inverting amplifier stage), which is made with an asymetric AOP ( 0 to 3,3 V).

So, I guess that its output cannot be negative as its input. This is what I see in simulation but not in measurement. Do you have any explanation ?

Thank you in advance,

I am simulating a TIA simulation stage followed by a non inverting amplifier stage. Between, there is a RC high pass filter to remove DC value.

The Fc of that filter is bad chosen (too high compared to the equivalent frequency of the pulse input) and generates a voltage under 0V at the queue of the pulse, as shown below).

This is then the input of the second stage (standard non inverting amplifier stage), which is made with an asymetric AOP ( 0 to 3,3 V).

So, I guess that its output cannot be negative as its input. This is what I see in simulation but not in measurement. Do you have any explanation ?

Thank you in advance,