wei9321

Member level 3

Ucc2813-0 & ucc28c43d question

ucc28c43 & ucc2813-0 datasheet as the fllowing:

**broken link removed**

**broken link removed**

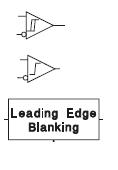

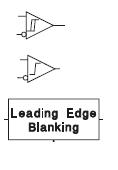

1.as fgure 1.what does it mean in the figure 1's BLOCK DIAGRAM ?

figure 1

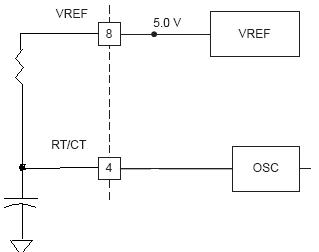

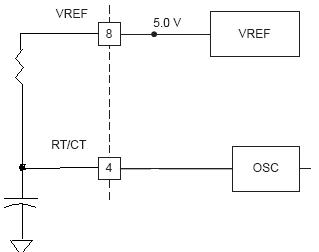

2.as figure 2,the vref pin and Ct/Rt pin connect capacitor and resistor can generate a triangle wave,why ?

figure 2

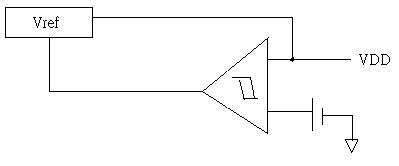

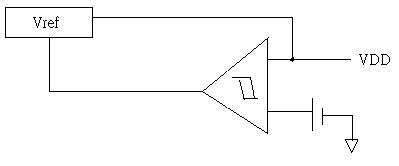

3.as figure 3,is the opa a comparator?

figure 3

thanks!

ucc28c43 & ucc2813-0 datasheet as the fllowing:

**broken link removed**

**broken link removed**

1.as fgure 1.what does it mean in the figure 1's BLOCK DIAGRAM ?

figure 1

2.as figure 2,the vref pin and Ct/Rt pin connect capacitor and resistor can generate a triangle wave,why ?

figure 2

3.as figure 3,is the opa a comparator?

figure 3

thanks!

Last edited: