yefj

Advanced Member level 4

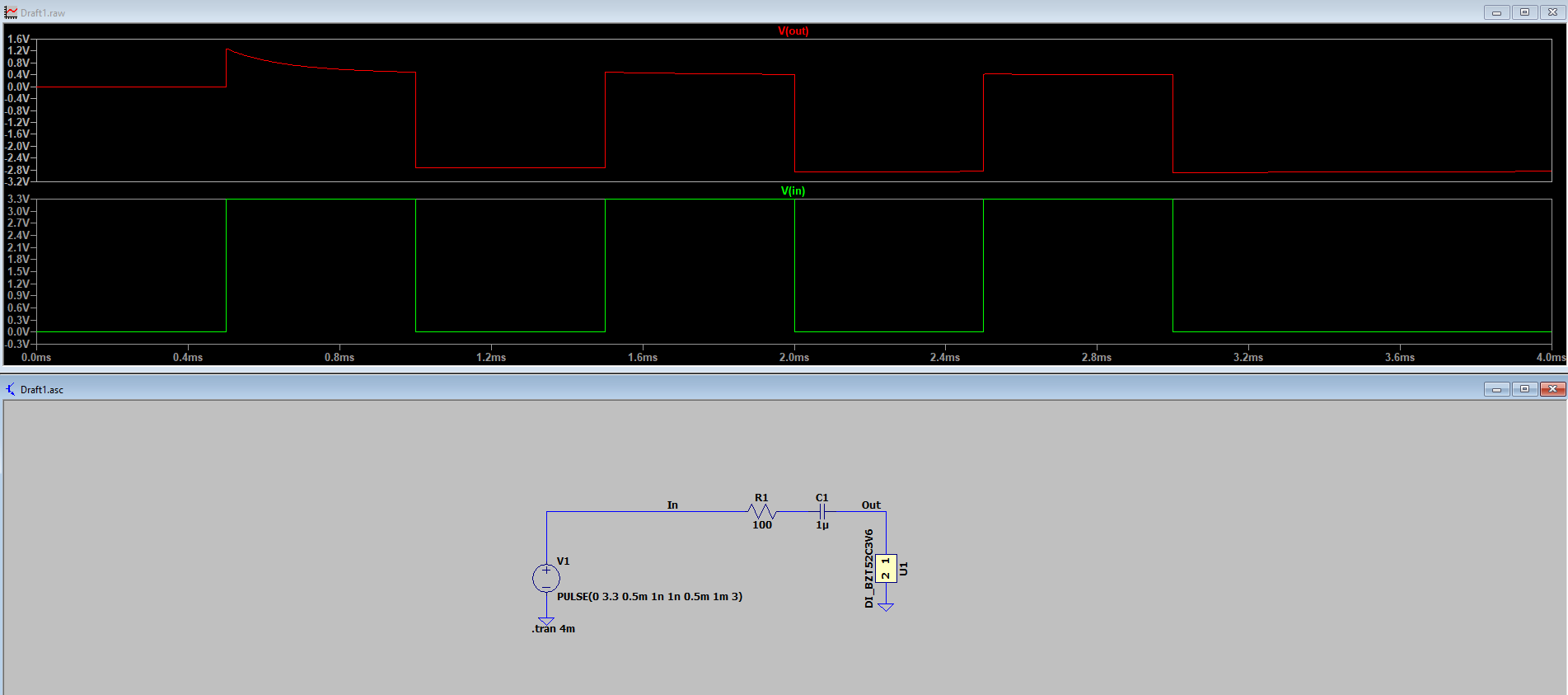

Hello, In the circuit bellow a Level shifter was made using Zenner diode.

However as you can see it drops only at the second pulse to the desired value.

Is there a way to make it do the level shifting from the first pulse?

Thanks.

However as you can see it drops only at the second pulse to the desired value.

Is there a way to make it do the level shifting from the first pulse?

Thanks.