mohamis288

Full Member level 3

Hello,

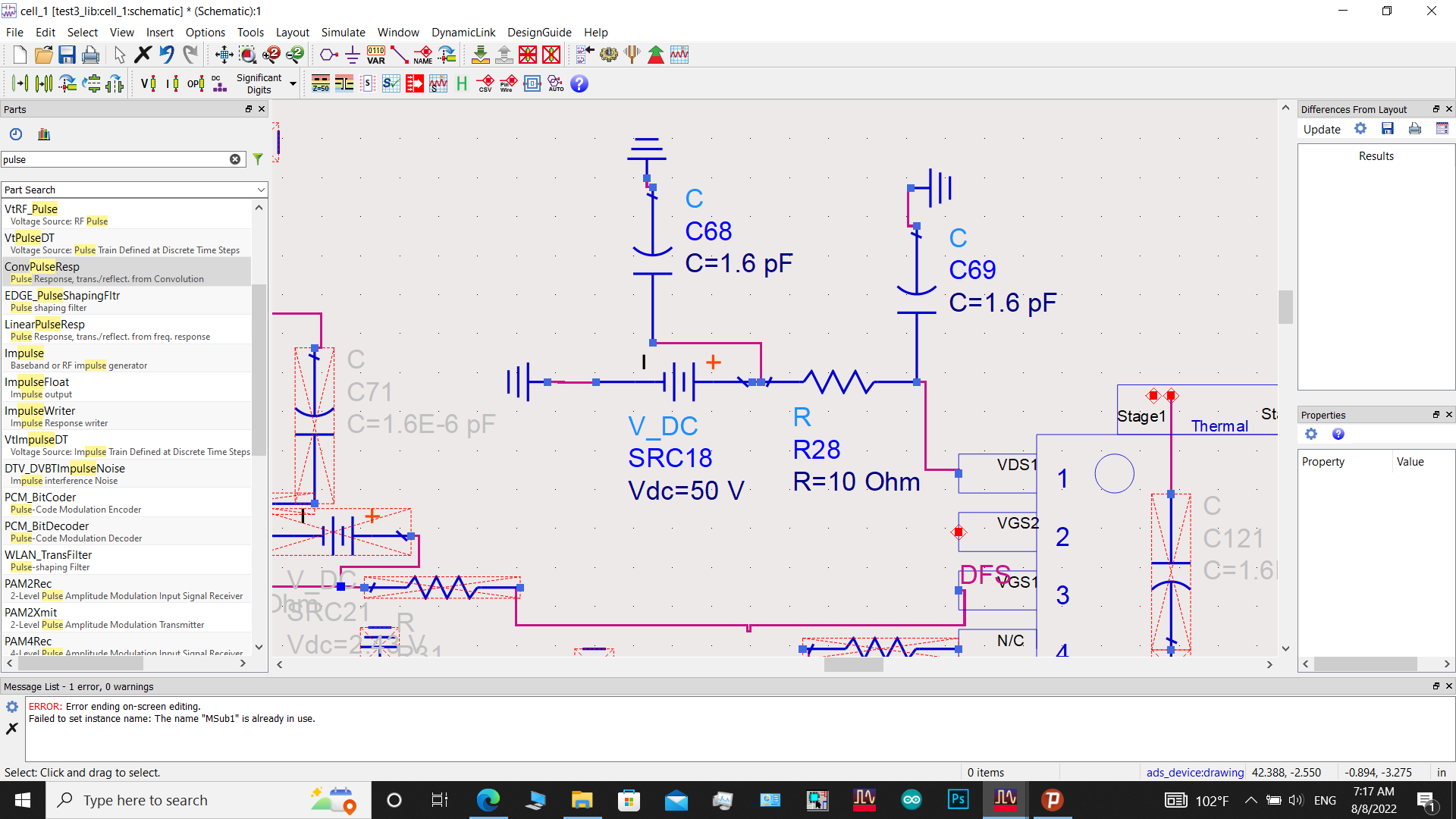

I am doing transient simulation on a circuit including a NXP IC large-signal model. I faced with a Time step error. after checking all the connection in my circuit, I realized that the problem occurred at the connection between DC supply and IC large-signal model. The picture this part of circuit is in the following:

"VDS1" is the mentioned node. Whatever I change the parameters in my simulation ( changing the capacitors value, resistor value, transient simulation parameters and etc), nothing will change. I do not have any problem with other DC connections, for instance, "VGS2", "VGS1", "VDS2". Do you have any solution for this?

I am doing transient simulation on a circuit including a NXP IC large-signal model. I faced with a Time step error. after checking all the connection in my circuit, I realized that the problem occurred at the connection between DC supply and IC large-signal model. The picture this part of circuit is in the following:

"VDS1" is the mentioned node. Whatever I change the parameters in my simulation ( changing the capacitors value, resistor value, transient simulation parameters and etc), nothing will change. I do not have any problem with other DC connections, for instance, "VGS2", "VGS1", "VDS2". Do you have any solution for this?