allennlowaton

Full Member level 5

Hello EDA felows,

I had made a corner simulation of this circuit and I found out that it failed on the SS corner.

I can't explain why.

Do I need a start-up circuit for this?

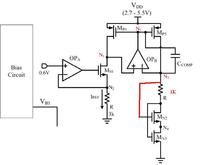

Below is the circuit diagram.

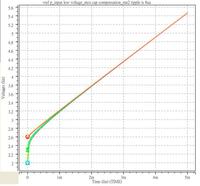

Below also are the pertinent node voltages.

The DC output voltages of OPA in all corners are the same.

Regards,

I had made a corner simulation of this circuit and I found out that it failed on the SS corner.

I can't explain why.

Do I need a start-up circuit for this?

Below is the circuit diagram.

Below also are the pertinent node voltages.

The DC output voltages of OPA in all corners are the same.

Regards,