mordak

Member level 5

Hi,

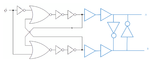

Implementing a non overlapping clock generator (NOCG) is fairly straightforward. But my problem is that the generated non-overlapped clocks are not symmetric (On time of the two non-overlapped clocks is slightly different). I read somewhere that adding an asymmetric transmission gate will help having symmetric clocks, but I could not get it work. I wonder if there is any NOCG circuit that gives symmetric output clocks.

Tnx

Implementing a non overlapping clock generator (NOCG) is fairly straightforward. But my problem is that the generated non-overlapped clocks are not symmetric (On time of the two non-overlapped clocks is slightly different). I read somewhere that adding an asymmetric transmission gate will help having symmetric clocks, but I could not get it work. I wonder if there is any NOCG circuit that gives symmetric output clocks.

Tnx