matrixofdynamism

Advanced Member level 2

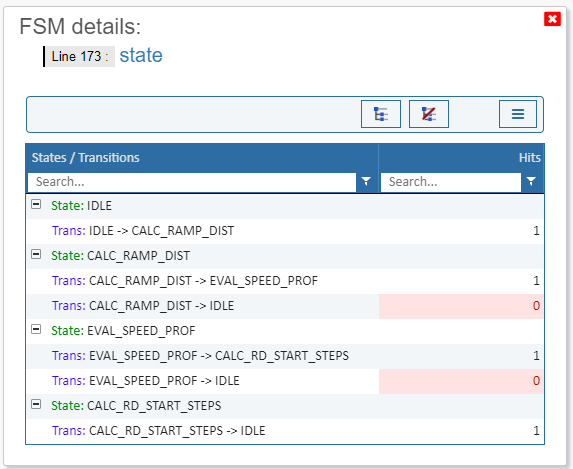

Here is a sample output from my coverage report:

For this module of interest, the state machine transitions like shown below every time. It spends one clock in each state except the IDLE state. It waits in IDLE state until a control signal is asserted.

IDLE -> CALC_RAMP_DIST -> EVAL_SPEED_PROF -> CALC_RD_START_STEPS -> IDLE

What confused me is why does the tool expect a path from the middle two states (CALC_RAMP_DIST and EVAL_SPEED_PROF) into IDLE when none exists. I then used the -fsmverbose flag in QuestaSim and found out that a path exists to IDLE state from these when reset is applied. This because when reset is applied, the state machine always goes into the IDLE state, regardless of what state it was in when reset was applied. This brings me to my problem.

Why does the tool require coverage into idle state from the middle states when the only way to get there is to apply reset? Shouldn't these transitions be excluded since they will never occur under "normal" circumstances and only when the design is put into reset? This problem is plaguing the FSM transition coverage in all parts of the VHDL RTL code.

For this module of interest, the state machine transitions like shown below every time. It spends one clock in each state except the IDLE state. It waits in IDLE state until a control signal is asserted.

IDLE -> CALC_RAMP_DIST -> EVAL_SPEED_PROF -> CALC_RD_START_STEPS -> IDLE

What confused me is why does the tool expect a path from the middle two states (CALC_RAMP_DIST and EVAL_SPEED_PROF) into IDLE when none exists. I then used the -fsmverbose flag in QuestaSim and found out that a path exists to IDLE state from these when reset is applied. This because when reset is applied, the state machine always goes into the IDLE state, regardless of what state it was in when reset was applied. This brings me to my problem.

Why does the tool require coverage into idle state from the middle states when the only way to get there is to apply reset? Shouldn't these transitions be excluded since they will never occur under "normal" circumstances and only when the design is put into reset? This problem is plaguing the FSM transition coverage in all parts of the VHDL RTL code.