kapil411

Newbie level 5

hiiiiiiii

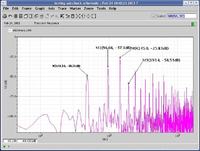

I'm working on sigma Delta ADC

CAN ANY1 PLEASE HELP ME ON WORKING WITH CADENCE SPECTRE FOR snr CALCULATION

TRANSIENT ANALYSIS DON E WITH

FIN=50HZ (OSR=64) (SINE WAVE)

FS=12800HZ=CLK FREQUENCY

HOW MANY CYCLES I SHOULD RUN THIS TRANSIENT ANALYSIS??

wats d funda of skipstart,skipstop, strobeperiod

& HOW TO CHOOSE

STROBEPERIOD?

SKIPSTART?

SKIPSTOP?

IN ORDER TO CALCULATE snr

PLEASE HELP ME IN FIGURING OUT THESE VALUES...

I'm working on sigma Delta ADC

CAN ANY1 PLEASE HELP ME ON WORKING WITH CADENCE SPECTRE FOR snr CALCULATION

TRANSIENT ANALYSIS DON E WITH

FIN=50HZ (OSR=64) (SINE WAVE)

FS=12800HZ=CLK FREQUENCY

HOW MANY CYCLES I SHOULD RUN THIS TRANSIENT ANALYSIS??

wats d funda of skipstart,skipstop, strobeperiod

& HOW TO CHOOSE

STROBEPERIOD?

SKIPSTART?

SKIPSTOP?

IN ORDER TO CALCULATE snr

PLEASE HELP ME IN FIGURING OUT THESE VALUES...