JonathanRalph

Newbie level 6

Hello all,

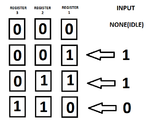

Let's say I have two registers declared, namely register A and register B. Both can store 1 bit (binary) of data. If I have an input of 1, register A should store a value of 1. If I supplied an input of 1 again, the data that was recently stored to A should jump to B and the new input would be stored to A. It's like a first in first out scenario, but with whole registers being involved. I coded my program this way:

...

...

I thought that the program would perform the first line before reading the second line. The result I expected was for B=0 (since it is initially zero) and A=1. But after executing the code, both A and B became 1. Any suggestions? (I'm still new to verilog btw)

Let's say I have two registers declared, namely register A and register B. Both can store 1 bit (binary) of data. If I have an input of 1, register A should store a value of 1. If I supplied an input of 1 again, the data that was recently stored to A should jump to B and the new input would be stored to A. It's like a first in first out scenario, but with whole registers being involved. I coded my program this way:

...

Code:

if (data_in==1)

begin

B=A;

A=1;

endI thought that the program would perform the first line before reading the second line. The result I expected was for B=0 (since it is initially zero) and A=1. But after executing the code, both A and B became 1. Any suggestions? (I'm still new to verilog btw)

Last edited by a moderator: