minhchau

Newbie level 6

Hi,

My chip has the digital section and analog section, to reduce influence noise from digital, the power and ground are separated.

I can see a real effect when it comes to power separation, but separating ground doesn't seen to have much effect.

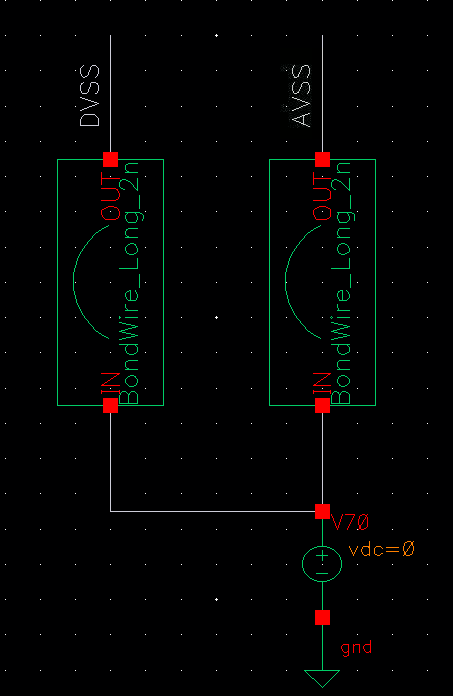

My set up DVSS and AVSS to verify separating ground showed as below:

DVSS is ground of digital section (2 bonding wire)

AVSS is ground of analog section (10 bonding wire)

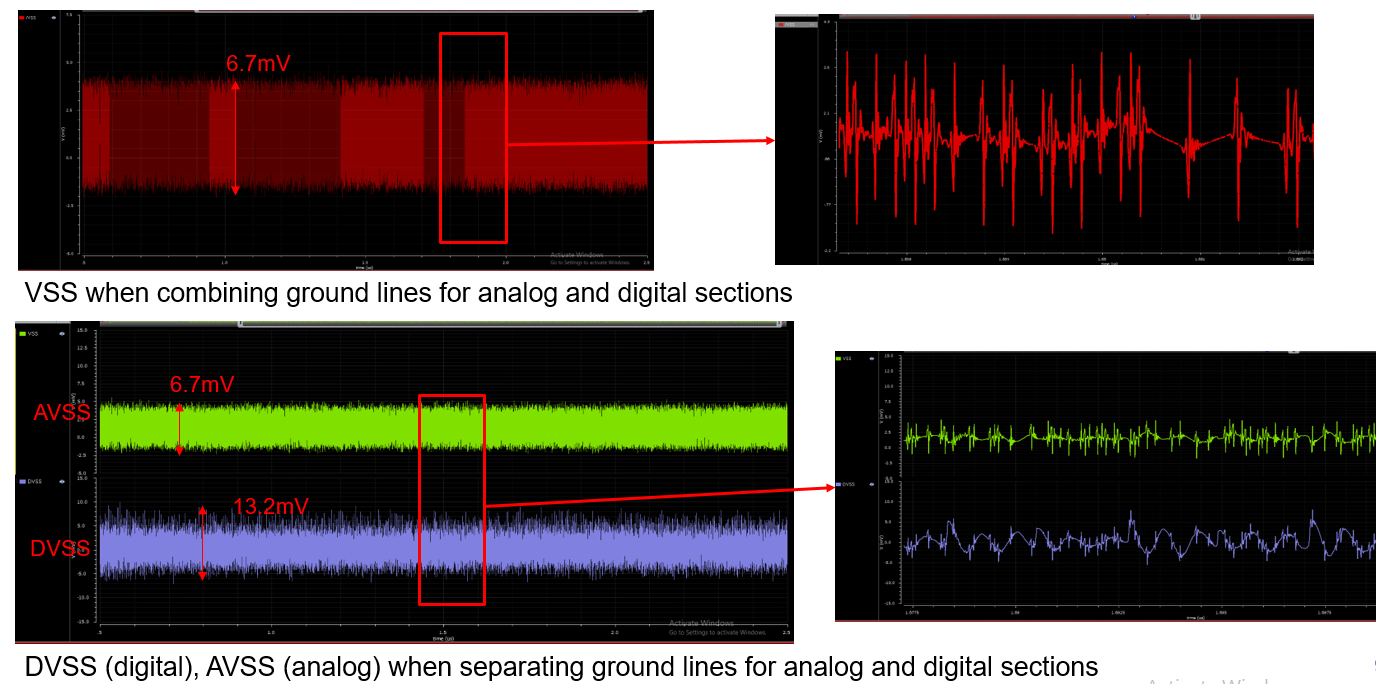

And there is simulation result:

The amplitude of AVSS is not much difference between combing and separating ground. So that, the performance does not change.

Is this result reasonable?

Are there somethin wrong with test bench?

Thanks

My chip has the digital section and analog section, to reduce influence noise from digital, the power and ground are separated.

I can see a real effect when it comes to power separation, but separating ground doesn't seen to have much effect.

My set up DVSS and AVSS to verify separating ground showed as below:

DVSS is ground of digital section (2 bonding wire)

AVSS is ground of analog section (10 bonding wire)

And there is simulation result:

The amplitude of AVSS is not much difference between combing and separating ground. So that, the performance does not change.

Is this result reasonable?

Are there somethin wrong with test bench?

Thanks