yefj

Advanced Member level 4

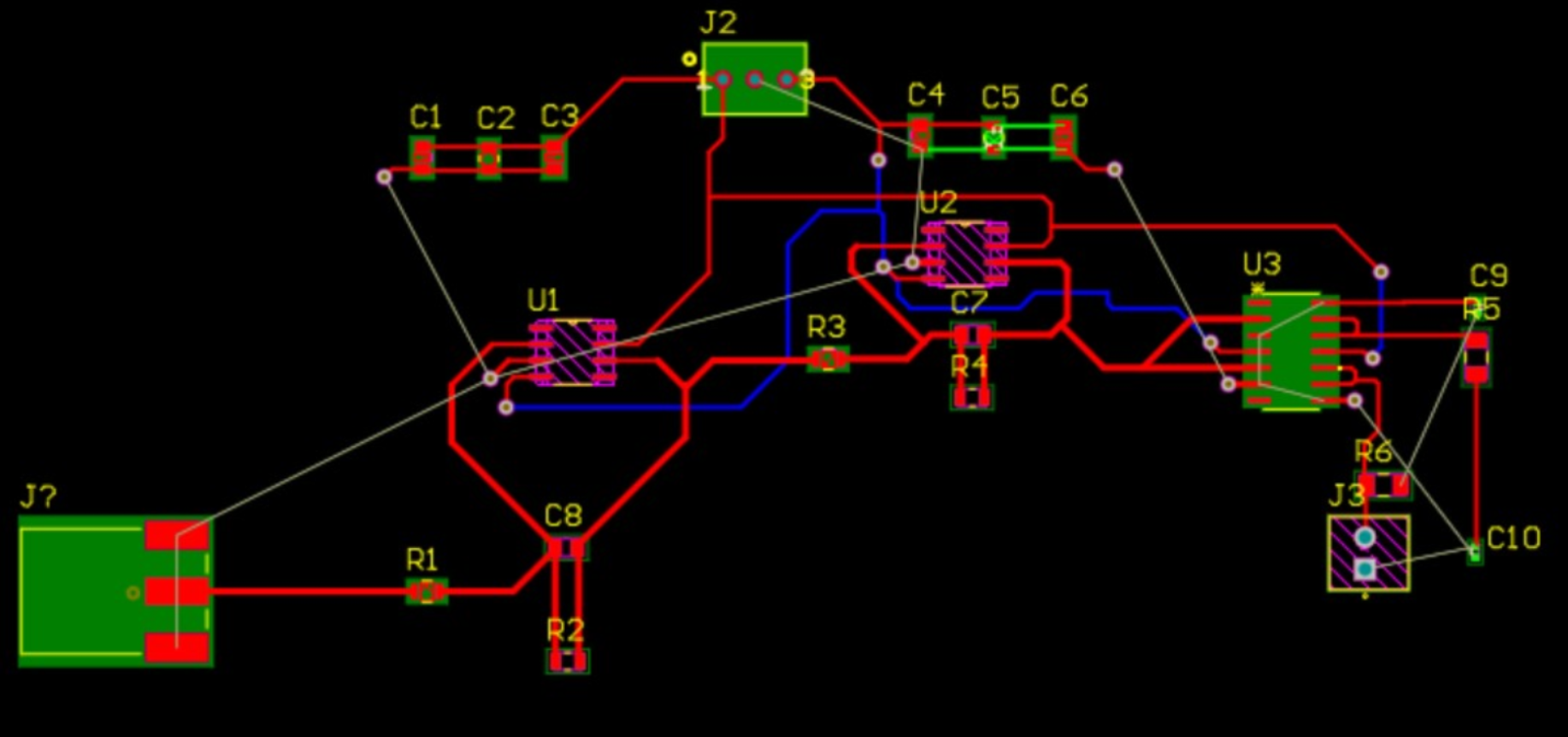

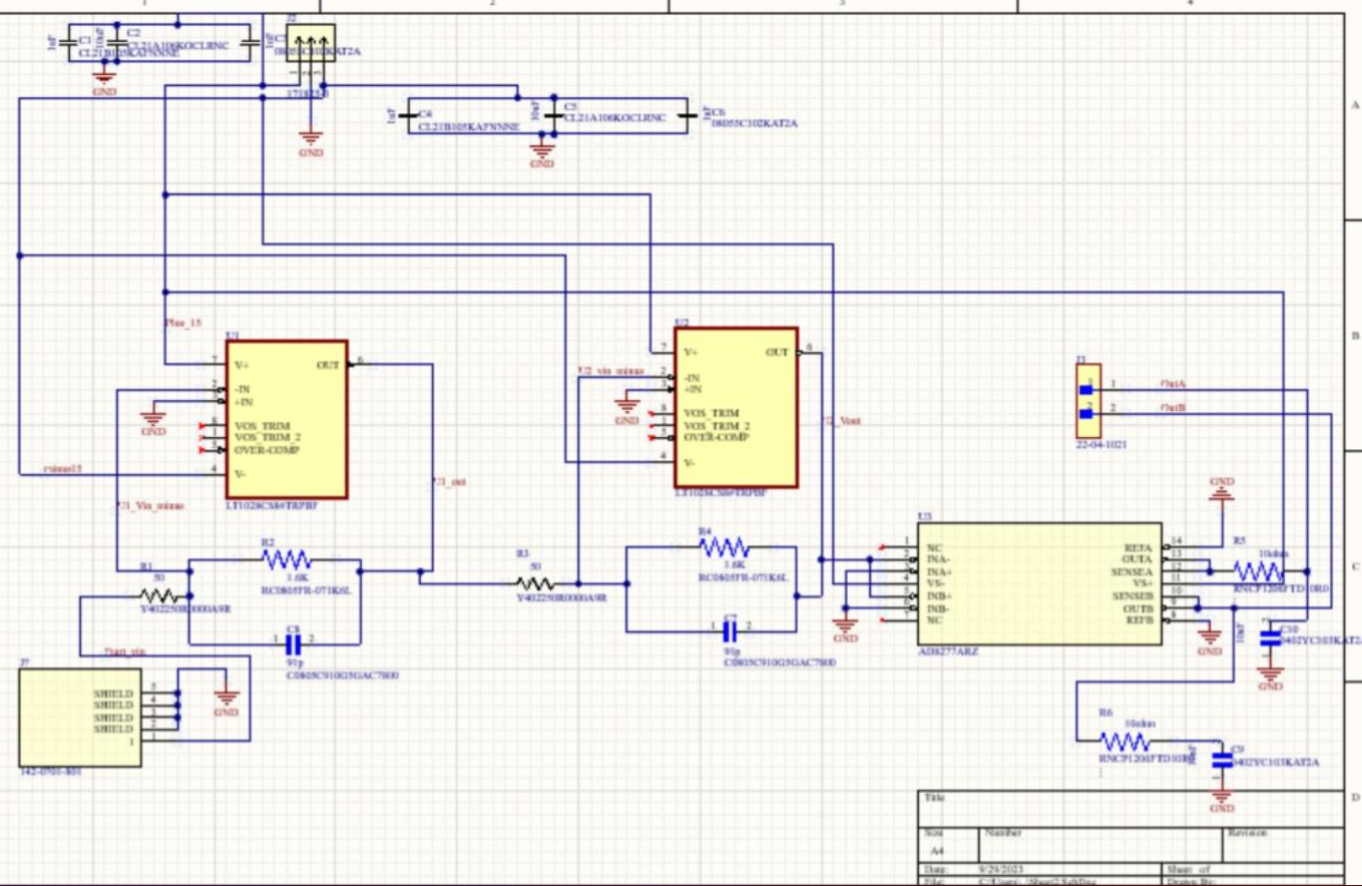

HelIo, have tried to convert my schemtics into PCB (before polygon pour). I got my traces looking very messy and its chaos. DC +15 -15 was done on the buttom layer too. I also need to do polygon pour after the traces will be ordered both on top and buttom layers ,the copper plates both will be GND net. Printscreens of my schematics and pcb shown below. My full project is attached in the link. I'll be glad to have so tip and methods on how i can improve the routing in the project.

I have few problems:

Thanks.

https://drive.google.com/file/d/1fSMrP67edmPFymSTFb0qWmbvB33Bv6_0/view?usp=sharing

I have few problems:

- my substrate is FR-4 1.6mm my connector pad width is 50 Ohm but the resistor pad is much smaller (higher impedance) i will have impedance mismatch,what should i do regarding connecting the connector with the resistor R1 ?

2.proper routing of the V+ and V- voltage traces?

Thanks.

https://drive.google.com/file/d/1fSMrP67edmPFymSTFb0qWmbvB33Bv6_0/view?usp=sharing