Debdut

Full Member level 3

Hello,

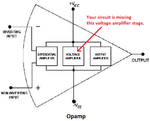

I have a two stage single output opamp. I want to create inverting and noninverting amplifiers and other circuits using the op amp.

How should the choose the resistance values that are connected at the input and feedback?

Opamp specs:

gain 75 dB

phase margin 55 degrees

unity gain bandwidth 750 MHz

slew rate 4.2 MV/s

VDD 1 V

dynamic range 0.32 - 0.7 V

current (diff. amp.) 3 uA

current (cs. amp.) 22 uA

feedback capacitor 500 fF

I have a two stage single output opamp. I want to create inverting and noninverting amplifiers and other circuits using the op amp.

How should the choose the resistance values that are connected at the input and feedback?

Opamp specs:

gain 75 dB

phase margin 55 degrees

unity gain bandwidth 750 MHz

slew rate 4.2 MV/s

VDD 1 V

dynamic range 0.32 - 0.7 V

current (diff. amp.) 3 uA

current (cs. amp.) 22 uA

feedback capacitor 500 fF