geozog86

Member level 3

Hello!

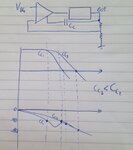

The attached is a loop of a regulator (I drew an extra stage as a square at the output).

There is an extra loop from the Cc capacitor.

I have to admit I have zero theoretical knowledge on how to analyze a circuit with two feedback loops.

Let's also assume that I cannot change the topology and/or remove Cc or something.

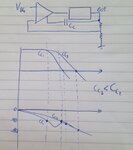

Loop stability simulation results are shown below it.

Strange observation 1: with increased Cc instead of getting a pole splitting effect and getting the dominant pole in lower frequencies, I get it in higher.

Strange observation 2: If I choose low enough Cc I get the effect of a second pole first, that then is cancelled by a zero, so I may look stable at UGBW point, but I get the dip you can see.

Questions:

1)on observation 1: How is that explained? Anyone has any idea?

2)on observation 2: If over corners the dip is "higher" than when I calculate my phase margin, am I safe? Or are such dips a huge risk and I should eliminate it to begin with?

Thanks for the help. Any expert on this giving an opinion, would be highly appreciated!

The attached is a loop of a regulator (I drew an extra stage as a square at the output).

There is an extra loop from the Cc capacitor.

I have to admit I have zero theoretical knowledge on how to analyze a circuit with two feedback loops.

Let's also assume that I cannot change the topology and/or remove Cc or something.

Loop stability simulation results are shown below it.

Strange observation 1: with increased Cc instead of getting a pole splitting effect and getting the dominant pole in lower frequencies, I get it in higher.

Strange observation 2: If I choose low enough Cc I get the effect of a second pole first, that then is cancelled by a zero, so I may look stable at UGBW point, but I get the dip you can see.

Questions:

1)on observation 1: How is that explained? Anyone has any idea?

2)on observation 2: If over corners the dip is "higher" than when I calculate my phase margin, am I safe? Or are such dips a huge risk and I should eliminate it to begin with?

Thanks for the help. Any expert on this giving an opinion, would be highly appreciated!