hejinjie

Newbie

- Joined

- Aug 8, 2009

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- Wuxi, Jiangsu, China

- Activity points

- 1,326

hi,

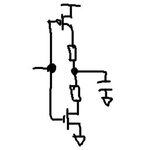

anyone got an idea to decrease the voltage of either rail of inverter output signal?

I need a 100mV~1.2V output signal and a 0V~1.12V output signal. Error within 10% @ 100mV and 1.12V.

can you help me with this design?

tinier, the better

Thanks in advance.

regards,

Kevin

anyone got an idea to decrease the voltage of either rail of inverter output signal?

I need a 100mV~1.2V output signal and a 0V~1.12V output signal. Error within 10% @ 100mV and 1.12V.

can you help me with this design?

tinier, the better

Thanks in advance.

regards,

Kevin