Ata_sa16

Full Member level 6

- Joined

- Mar 29, 2016

- Messages

- 343

- Helped

- 59

- Reputation

- 118

- Reaction score

- 58

- Trophy points

- 28

- Location

- Milky Way Galaxy, 179° 56′ 39.4″

- Activity points

- 2,221

Hi all,

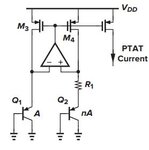

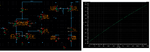

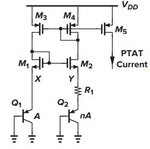

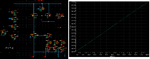

I have been struggling with this PTAT current source.

It works fine but problem is, it does not have enough slope. I did a lot of tuning but I never got better than this.

Do you have any suggestions ? it can be totally different circuit. I just need a PTAT bias current source with higher slope.

Thank your for your time.

I appreciate.

I have been struggling with this PTAT current source.

It works fine but problem is, it does not have enough slope. I did a lot of tuning but I never got better than this.

Do you have any suggestions ? it can be totally different circuit. I just need a PTAT bias current source with higher slope.

Thank your for your time.

I appreciate.