shanmei

Advanced Member level 1

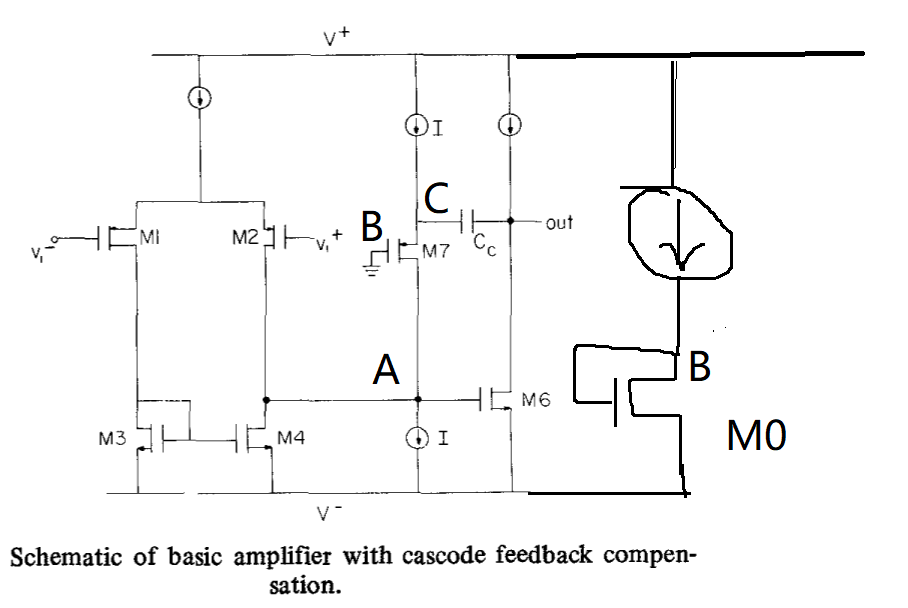

This is the famous opamp architecture with good negative supply (V-) PSRR. M7 blocks the the ac signal from node A to C. There is a condition that the bias node B, the gate of M7, should be ideal, with no ac signal.

If I use a diode connection M0 bias node B. Then there is ac signal from V- will couple to B, and C, leading to a bad PSRR.

How to make bias voltage B with no ac signal?? Thanks.

paper source:

If I use a diode connection M0 bias node B. Then there is ac signal from V- will couple to B, and C, leading to a bad PSRR.

How to make bias voltage B with no ac signal?? Thanks.

paper source: