zhangz64

Junior Member level 3

Hi Everyone,

I am trying to design a programmable current sink with range from 0mA to 1mA.

The current sink is used to sink current from the a PMOS current mirror, therefore the voltage at output should be around 0.3V.

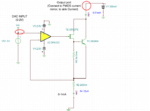

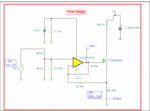

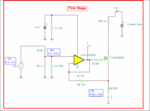

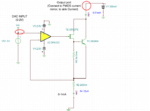

I designed the circuit with a DAC followed by a Voltage to Current convertor circuit[Adapted from a reference TI design].

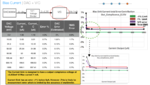

The circuit worked well normally, but It does not work if the output port have a voltage lower than 1V.

I tried to tied the ground to a negative rail , but I was told that is not safe for the PMOS current mirror.

I also check the current DAC, All the current DAC i found have compliance voltage for output which is typically higher than 0.5V.

Also, Their range is hardly what i wanted.

i am kind of running out options now. I would really appreciate some input here.

So is there any way to modify my existing circuit to make it work for 0.3V output? (Attached below). [I think the reason the circuit did not work is because of the Vd of the NMOS is almost equal to the Vs of the NMOS at low output voltage. therefore no current being pushed through.]

Or if possible please suggest a better solution for this.

Thanks a lot for your help,

Best,

Eddy

I am trying to design a programmable current sink with range from 0mA to 1mA.

The current sink is used to sink current from the a PMOS current mirror, therefore the voltage at output should be around 0.3V.

I designed the circuit with a DAC followed by a Voltage to Current convertor circuit[Adapted from a reference TI design].

The circuit worked well normally, but It does not work if the output port have a voltage lower than 1V.

I tried to tied the ground to a negative rail , but I was told that is not safe for the PMOS current mirror.

I also check the current DAC, All the current DAC i found have compliance voltage for output which is typically higher than 0.5V.

Also, Their range is hardly what i wanted.

i am kind of running out options now. I would really appreciate some input here.

So is there any way to modify my existing circuit to make it work for 0.3V output? (Attached below). [I think the reason the circuit did not work is because of the Vd of the NMOS is almost equal to the Vs of the NMOS at low output voltage. therefore no current being pushed through.]

Or if possible please suggest a better solution for this.

Thanks a lot for your help,

Best,

Eddy