Rajinder1268

Full Member level 3

Hi all,

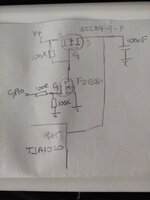

I have attached a circuit and need some feedback. I need to disconnect and reconnect the Vsupply (12V filtered from.car battery) to a LIN transceiver (tja1020) I have used a n channel device to pull the gate of the p channel fet under the control of a microcontroller GPIO.

The p channel device is BSS84-7-F and the n channel fet is FDV303N. The n channel is a logic level fet. I wanted to ask if there is anything that looks incorrect on my circuit and if so what the remedy would be. Also if there is an easier way of disconnecting the supply.

I have attached a circuit and need some feedback. I need to disconnect and reconnect the Vsupply (12V filtered from.car battery) to a LIN transceiver (tja1020) I have used a n channel device to pull the gate of the p channel fet under the control of a microcontroller GPIO.

The p channel device is BSS84-7-F and the n channel fet is FDV303N. The n channel is a logic level fet. I wanted to ask if there is anything that looks incorrect on my circuit and if so what the remedy would be. Also if there is an easier way of disconnecting the supply.