bellona

Junior Member level 2

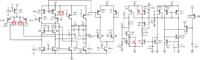

Hi, everyone. One of the op-amps in my chip isn't functioning all right. The opamp is a fully differential opamp with folded cascode PMOS input stage. The Pre and Post-simulation shows nothing wrong, it's schematic is:

I'm using a 0.35um 2p4m salicide process with non-epi substrate, VDD is 3.3V. When ever the gate voltage of the input PMOS pair (MP0 & MP1) is below 1.5V, the output of this opamp would suddenly drop to almost 0V, otherwise it would function allright, either in single to differential or inverting amplify configuration.

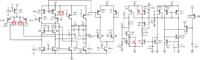

When the output drops, the current consumption of this opamp increases by about 400uA. I suspect some mild latchup might have occured which have increased the current dumping into the drain of MN3 and MN15, hence increasing the voltage at the drain of MN0 and MN1. The layout of the input differential pair is:

MP0 and MP1 is cross-coupled in 1221 fashion. NWELL1 is the n-well of MP0 and MP1, NTAP1 is the associated NTAP of these nwells, which are way too sparsely, the distance between the adjancent NTAPs in the same nwell is 40um (Design rule suggested a maximum distance of 30um). NTAP2 (built by nwell) is a nearby guardring connecting to VDD (3.3V).

Since the nwell (NWELL1) of the input transistor is not tapped right, is it possible a mild latchup might occur when the voltage of this well is lowered which dumps current into this well? Thanks in advance!

I'm using a 0.35um 2p4m salicide process with non-epi substrate, VDD is 3.3V. When ever the gate voltage of the input PMOS pair (MP0 & MP1) is below 1.5V, the output of this opamp would suddenly drop to almost 0V, otherwise it would function allright, either in single to differential or inverting amplify configuration.

When the output drops, the current consumption of this opamp increases by about 400uA. I suspect some mild latchup might have occured which have increased the current dumping into the drain of MN3 and MN15, hence increasing the voltage at the drain of MN0 and MN1. The layout of the input differential pair is:

MP0 and MP1 is cross-coupled in 1221 fashion. NWELL1 is the n-well of MP0 and MP1, NTAP1 is the associated NTAP of these nwells, which are way too sparsely, the distance between the adjancent NTAPs in the same nwell is 40um (Design rule suggested a maximum distance of 30um). NTAP2 (built by nwell) is a nearby guardring connecting to VDD (3.3V).

Since the nwell (NWELL1) of the input transistor is not tapped right, is it possible a mild latchup might occur when the voltage of this well is lowered which dumps current into this well? Thanks in advance!