MissP.25_5

Newbie level 6

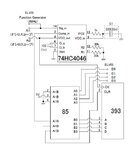

Please tell me in detail which wire should go to which number (eg. A1, B2, C4 etc...).

I am in need of big help here. I don't know what else should be done to get this correct.

I have to build this PLL circuit and choose any 3 N (integer) of the N-divider. Then I have to observe the input signal Sig_in and the output signal VC

I took 4 pictures of different angles so you can see better. Click on the flickr links to see the pictures of my circuit. Click on the picture to zoom in.

https://www.flickr.com/photos/98820721@N04/11870437296/sizes/o/in/photostream/

https://www.flickr.com/photos/98820721@N04/11870033074/sizes/h/in/photostream/

https://www.flickr.com/photos/98820721@N04/11870445586/sizes/k/in/photostream/

https://www.flickr.com/photos/98820721@N04/11869882813/sizes/k/in/photostream/