aryajur

Advanced Member level 3

- Joined

- Oct 23, 2004

- Messages

- 793

- Helped

- 124

- Reputation

- 248

- Reaction score

- 37

- Trophy points

- 1,308

- Location

- San Jose, USA

- Activity points

- 7,788

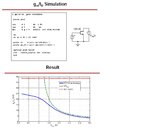

The 1st graph, try sweeping the current to a larger value say 500uA or 1mA to see the full curve. I don't know what the size of the MOS is maybe you are not getting out of subthreshold with 1uA of current.

When they say gm/Id is region independent I think they only mean its independent of subthreshold-weak inversion-saturation. When the MOS goes into triode the the gm/Id curves I saw were not very consistent and varied all over the place as soon as I started nearing subthreshold.

What is Iref in the 1st graph? Is it the sweeping DC current source? If that is the case then when you plot gmoverid vs Id/(W/L) that should only change the scale of the x-axis and not the shape of the graph since W/L is constant throughout the sweep, right?

So it could be that something is going wrong in the Cadence plotting AWD. I myself could never get the plots to work in Cadence alone since it kept messing up when I changed the x-axis, I then simply ended up exporting the data to MATLAB/excel and did the plots much more easily.

When they say gm/Id is region independent I think they only mean its independent of subthreshold-weak inversion-saturation. When the MOS goes into triode the the gm/Id curves I saw were not very consistent and varied all over the place as soon as I started nearing subthreshold.

What is Iref in the 1st graph? Is it the sweeping DC current source? If that is the case then when you plot gmoverid vs Id/(W/L) that should only change the scale of the x-axis and not the shape of the graph since W/L is constant throughout the sweep, right?

So it could be that something is going wrong in the Cadence plotting AWD. I myself could never get the plots to work in Cadence alone since it kept messing up when I changed the x-axis, I then simply ended up exporting the data to MATLAB/excel and did the plots much more easily.