AllenD

Member level 5

Hi All,

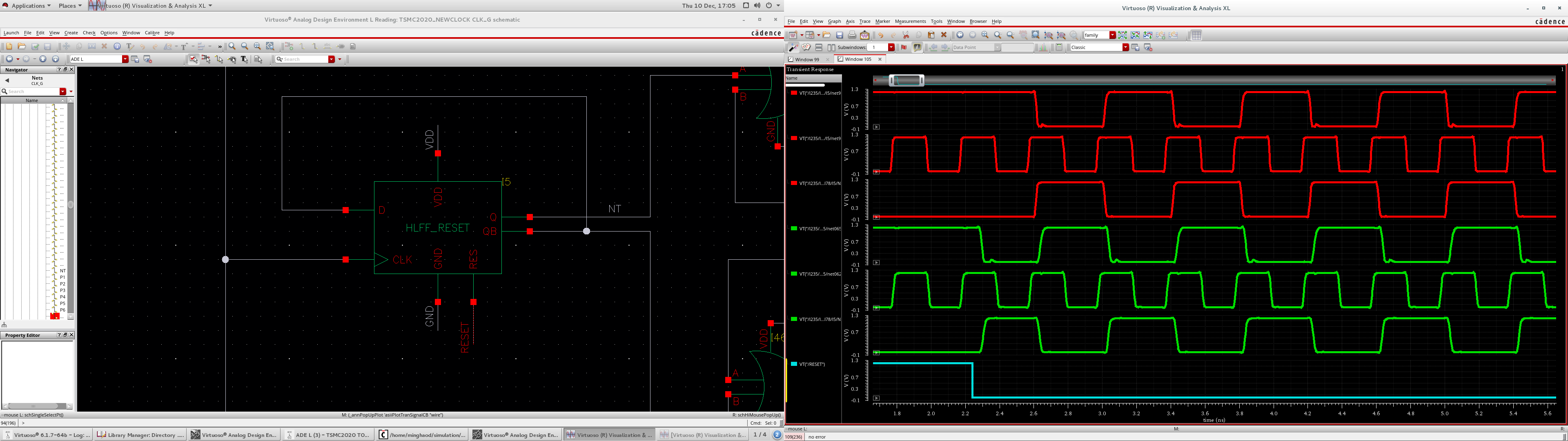

I am using a Hybrid Latch Flip-Flop (HLFF) circuit work as a D-flipflop, and feedback from Q_b to D to realize a freq divide by 2 circuit.

My question is how to regulate the initial phase?

In the attached pic on the left is the HLFF with reset and feedback. On the right:

1. Blue is the reset signal.

2. For the red group, the signals are D, CLK, Q in order (the first line is D, the second line is CLK and the third line is Q ). Same for the Green group

3. The difference of red and green is that I use a different transistor from PDK to simulate the exact HLFF circuit topology.

You can see in both cases, the CLK signal (the 2nd and 5th signal in plot) of red and green are the same. But the difference is the starting phase of the output. For red, Q rise with the 3rd, 5th, and 7th rising edge of CLK but in green, Q rise with the 2nd, 4th, and 6th rising edge of CLK.

As result, the Q of red and green are the opposite.

Can you please let me know how to prevent this phenomenon?

Thanks

Al

I am using a Hybrid Latch Flip-Flop (HLFF) circuit work as a D-flipflop, and feedback from Q_b to D to realize a freq divide by 2 circuit.

My question is how to regulate the initial phase?

In the attached pic on the left is the HLFF with reset and feedback. On the right:

1. Blue is the reset signal.

2. For the red group, the signals are D, CLK, Q in order (the first line is D, the second line is CLK and the third line is Q ). Same for the Green group

3. The difference of red and green is that I use a different transistor from PDK to simulate the exact HLFF circuit topology.

You can see in both cases, the CLK signal (the 2nd and 5th signal in plot) of red and green are the same. But the difference is the starting phase of the output. For red, Q rise with the 3rd, 5th, and 7th rising edge of CLK but in green, Q rise with the 2nd, 4th, and 6th rising edge of CLK.

As result, the Q of red and green are the opposite.

Can you please let me know how to prevent this phenomenon?

Thanks

Al