Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Code C - [expand] // result += 3087

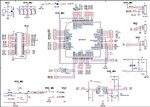

1) ADS1118 A1N1 is connected ground so the disturbance coming from the GND plane would be removed.

unsigned short int result1 = 0;

double digi_result1 = 0;

CS = LOW;

WriteSPI2(0xF003); // FOO3 when AIN3 is AINp and AIN2 is GND

while(!SPI2STATbits.SPIRBF);

result1 = ReadSPI2();

WriteSPI2(0xF00B);

while(!SPI2STATbits.SPIRBF);

ReadSPI2(); // dummy read of config register read back format and output result

while(PORTGbits.RG7); // Wait for DOUT/#DRDY to go low

CS = HIGH;

// printf("B1 = %u\n",result1);

if( result1 & 0x8000 )

digi_result1 = 0;

else

digi_result1 = digi_result1 + (((float)result1 * 6.144) / 32767U);

printf(" V1 = %.4f mV\n",(double)digi_result1);

digi_result1 =0;

result1 = 0;

CS = LOW;

WriteSPI2(0xE003); // E003 when AIN2 is AINp, FOO3 when AIN3 is AINp

while(!SPI2STATbits.SPIRBF);

result1 = ReadSPI2();

WriteSPI2(0xE003);

while(!SPI2STATbits.SPIRBF);

ReadSPI2(); // dummy read of config register read back format and output result

while(PORTGbits.RG7);

CS = HIGH;