Nasib.Fahim

Newbie level 4

Hi all. I have a problem.

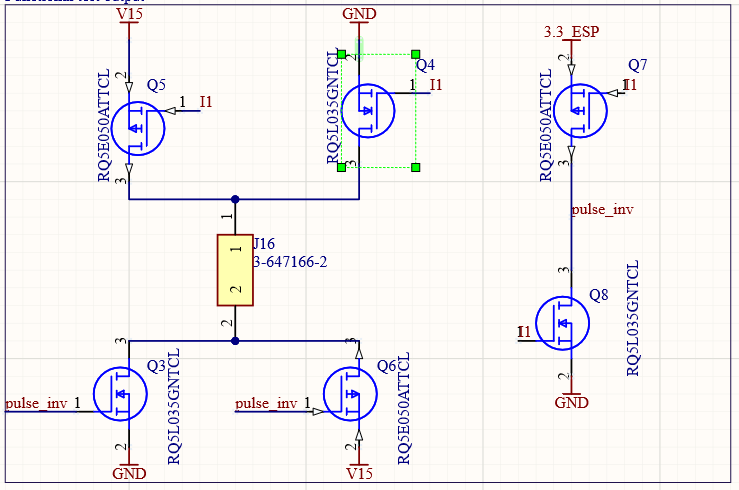

I am using this circuit to invert the current sense just with one command line (I1).

If i use this circuit as it is, somehow i am seeing a short circuit somewhere. If i reduce the 15V to 5V the circuit works correctly.

Could anyone help me please ?

Thanks a lot!!

I am using this circuit to invert the current sense just with one command line (I1).

If i use this circuit as it is, somehow i am seeing a short circuit somewhere. If i reduce the 15V to 5V the circuit works correctly.

Could anyone help me please ?

Thanks a lot!!